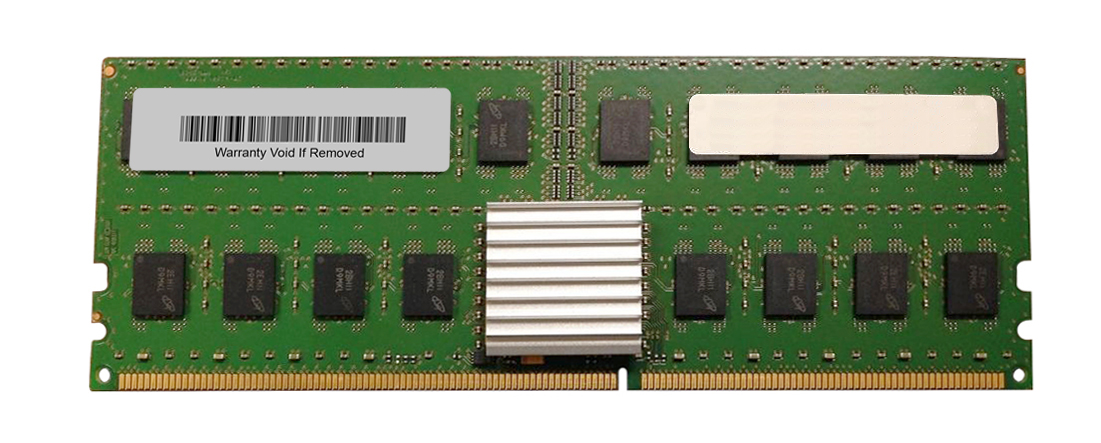

Ddr2 synch dram

Supreme shock-resistant qualities ensure superior protection for data stored on the drive.

In addition to double pumping the data bus as in DDR SDRAM transferring data on the rising and falling edges of the bus clock signal , DDR2 allows higher bus speed and requires lower power by running the internal clock at half the speed of the data bus. The two factors combine to produce a total of four data transfers per internal clock cycle. Alternatively, DDR2 memory operating at twice the external data bus clock rate as DDR may provide twice the bandwidth with the same latency. Both performed worse than the original DDR specification due to higher latency, which made total access times longer. These chips are mostly standard DDR chips that have been tested and rated to be capable of operation at higher clock rates by the manufacturer.

Ddr2 synch dram

Traditionally, dynamic random access memory DRAM had an asynchronous interface, which means that it responds as quickly as possible to changes in control inputs. This allows the memory chip to have a more complex pattern of operation than an asynchronous DRAM. DDR stands for double data rate, which means the chip reads or writes two words of data per clock cycle. The DDR interface accomplishes this by reading and writing data on both the rising and falling edges of the clock signal. In addition, some minor changes to the SDR interface timing were made in hindsight, and the supply voltage was reduced from 3. In a computer system, the clock signal is an oscillating frequency used to coordinate interaction between digital circuits. Simply put, it synchronizes communication. Digital circuits designed to operate on the clock signal may respond at the rising or falling edge of the signal. DDR5 is in development. The clock speed for the memory chip should be synchronous with the computer's system bus. Nick Jasuja has over 15 years of technology industry experience, including at Amazon in Seattle.

If the requested column address is at the start of a block, both burst modes sequential and interleaved return data in the same sequential sequence

DRAM integrated circuits ICs produced from the early s to early s used an asynchronous interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways. SDRAM has a synchronous interface, whereby changes on control inputs are recognised after a rising edge of its clock input. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. The memory is divided into several equally sized but independent sections called banks , allowing the device to operate on a memory access command in each bank simultaneously and speed up access in an interleaved fashion. Pipelining means that the chip can accept a new command before it has finished processing the previous one.

Search Everywhere Threads This forum This thread. Search titles only. Search Advanced search…. Everywhere Threads This forum This thread. Search Advanced…. Log in. Install the app.

Ddr2 synch dram

Implementations often have to use schemes such as phase-locked loops and self-calibration to reach the required timing accuracy. One advantage of keeping the clock frequency low is that it reduces the signal integrity requirements on the circuit board connecting the memory to the controller. The first specification is for memory chips, and the second is for memory modules. To increase memory capacity and bandwidth, chips are combined on a module. For instance, the bit data bus for DIMM requires eight 8-bit chips, addressed in parallel. Multiple chips with common address lines are called a memory rank. The term was introduced to avoid confusion with chip internal rows and banks.

Antonyms of seal

For reference, a row of a 1 Gbit [6] DDR3 device is 2, bits wide, so internally 2, bits are read into 2, separate sense amplifiers during the row access phase. The DDR interface accomplishes this by reading and writing data on both the rising and falling edges of the clock signal. Smithsonian Institution. There are several limits on DRAM performance. Analog recording. In other projects. In other projects. To make more of this bandwidth available to users, a double data rate interface was developed. Type of RAM. This operation has the side effect of refreshing the dynamic capacitive memory storage cells of that row. Archived PDF from the original on This uses the same commands, accepted once per cycle, but reads or writes two words of data per clock cycle. It is the duty of the memory controller to ensure that the SDRAM is not driving read data on to the DQ lines at the same time that it needs to drive write data on to those lines.

Some confusion has been created due to the difference in the listings for speed "MHz" , and the way memory is described from a sales standpoint " personal computer XXXXXX ". The listings below should resolve any confusion.

Contents move to sidebar hide. The fraction which is refreshed is configured using an extended mode register. It was commercially introduced as a 16 Mbit [6] memory chip by Samsung Electronics in DDR2 started to become competitive against the older DDR standard by the end of , as modules with lower latencies became available. A write command is accompanied by the data to be written driven on to the DQ lines during the same rising clock edge. Retrieved 19 June DDR4 adds four new Bank Groups technology. This is because data written to the DRAM must be presented in the same cycle as the write command, but reads produce output 2 or 3 cycles after the read command. It is possible to refresh a RAM chip by opening and closing activating and precharging each row in each bank. You may see more details at Cookie Statement. For a pipelined read, the requested data appears a fixed number of clock cycles latency after the read command, during which additional commands can be sent. While self-refresh mode consumes slightly more power than power-down mode, it allows the memory controller to be disabled entirely, which commonly more than makes up the difference. You could click Agree to accept cookies or Disagree to reject cookies. Slower clock cycles will naturally allow lower numbers of CAS latency cycles. Contents move to sidebar hide.

0 thoughts on “Ddr2 synch dram”